## Функциональная верификация микропроцессоров

A.C. Камкин kamkin@ispras.ru

#### Содержание лекции

- Введение

- □ Проектирование микропроцессоров

- □ Языки описания аппаратуры

- Уровни верификации

- Основные подходы

- Имитационная верификация (тестирование)

- Генерация тестовых программ

- Формальная верификация

- Проекты ИСП РАН

- □ Проект C++TESK

- □ Проект MicroTESK

- □ Открытые проблемы

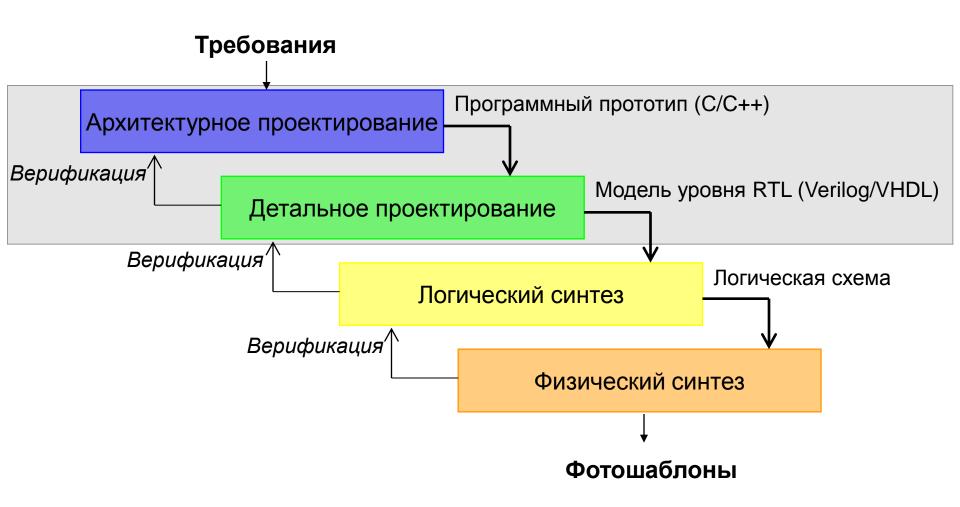

#### Проектирование микропроцессоров

#### Ошибки проектирования

Число ошибок ≈ 10 000 (Pentium 4)

Цена ошибки ≈ 500 000 000 \$ (Pentium)

Сложность микропроцессоров растет

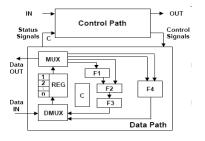

## Модульная и системная верификация

#### Модульная верификация

#### Проверяется модель отдельного модуля

#### через входные и выходные сигналы

#### Системная верификация

#### Проверяется модель всего микропроцессора

#### с помощью тестовых программ

lui s1, 0x2779

ori s1, s1, 0xc8b9

lui s3, 0x4ee

ori s3, s3, 0xf798

add v0, a0, a2

sub t1, t3, t5

add t7, s1, s3

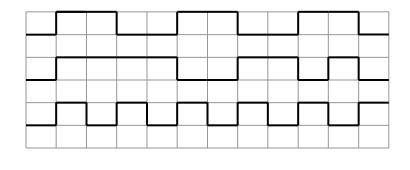

## Языки описания аппаратуры (HDL)

```

input S;

CLK

output R1, R2;

S

void design() {

R1

while(true) {

R2

wait(S); —

delay(6);———

6 тактов

R1 = 1;

delay(1);

R1 = 0;

delay(1);

R2 = 1;

delay(1);

R2 = 0;

Одновременные присваивания

V1 = 1;

} }

```

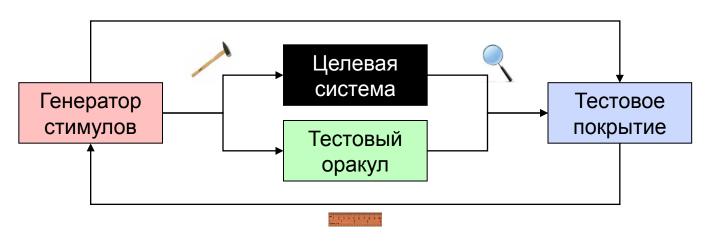

## Имитационная верификация

## Задачи имитационной верификации

- Генерация стимулов

- Проверка реакций

- Оценка покрытия

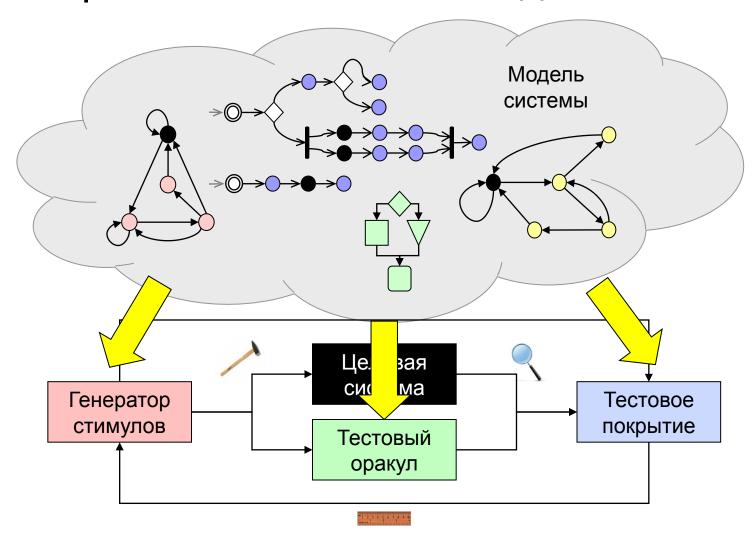

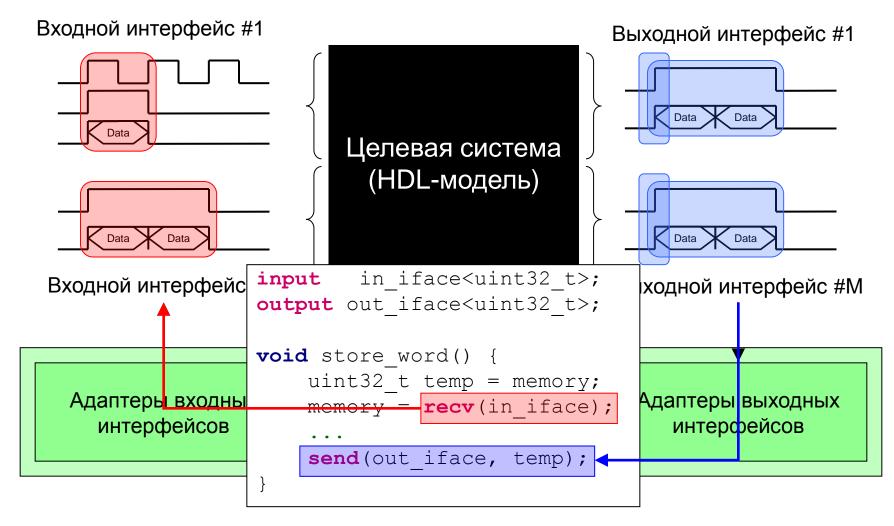

## Тестирование на основе моделей

## Адаптеры интерфейсов

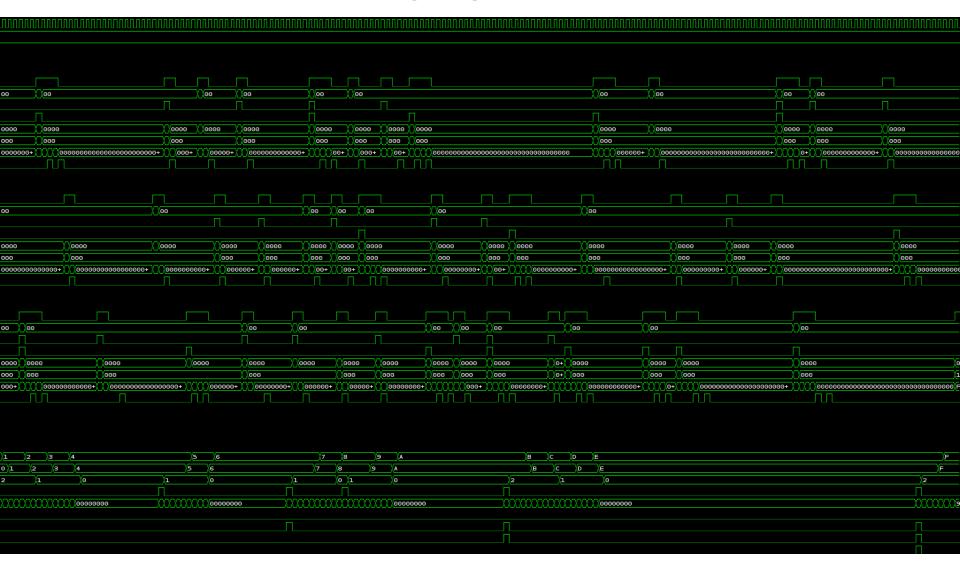

#### Генерация тестовых программ

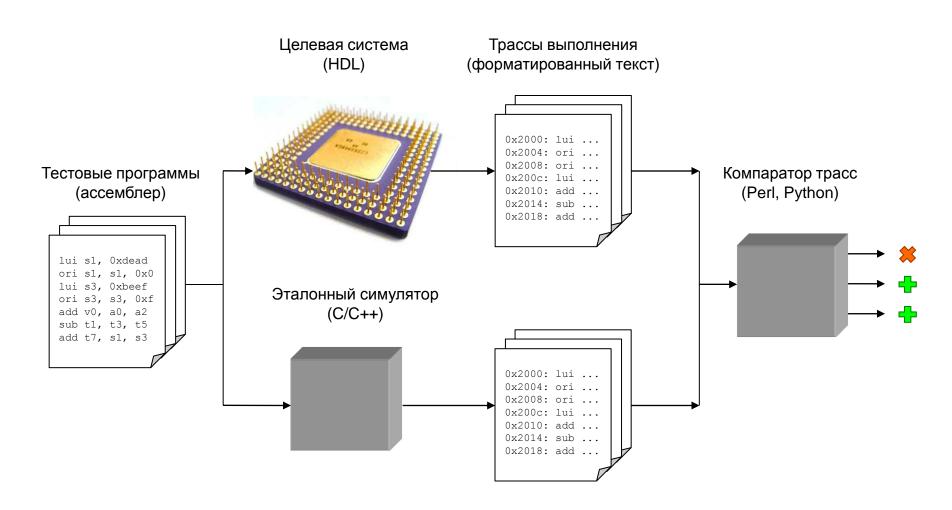

## Генерация тестов на основе моделей

#### Шаблон тестовой программы

```

Variable: addr = 0x100

Variable: req

Bias: Resource-Dependency (GPR) = 30 \mid 100 = 7, 110 = 25,..., 1F0 = 16

Bias: Alignment (4) = 50

Instruction: Load R5 <- ?

Bias: Alignment (16) = 100

Repeat (addr < 0x200)

Instruction: Store reg -> addr

Select

Instruction: Add ? <- reg + ?</pre>

Bias: SumZero

Instruction: Sub ? <- ? - ?</pre>

addr = addr + 0x10

```

#### Тестовая программа

```

Resource Initial Values:

R6 = 8, R3 = -25,..., R17 = -16

Instructions:

500: Load R5 <- FF0

504: Store R4 -> 100

508: Sub R5 <- R6 - R4

50C: Store R4 -> 110

510: Add R6 < - R4 + R3

57C: Store R4 \rightarrow 1F0

580: Add R9 <- R4 + R17

```

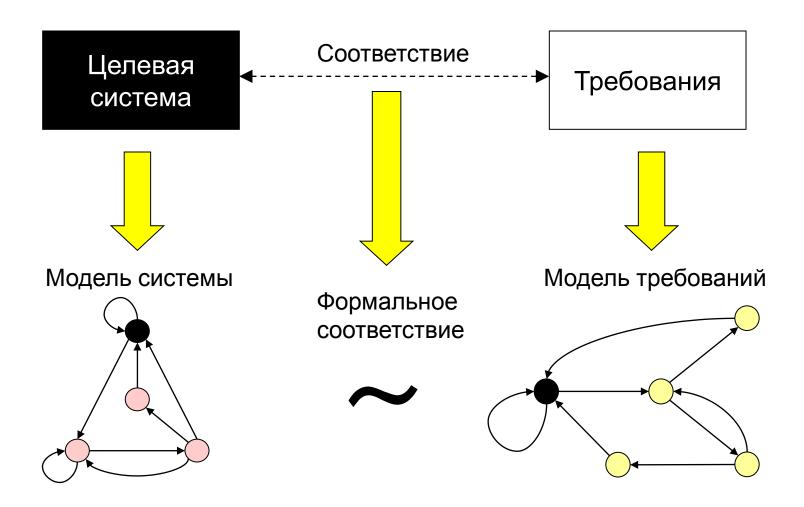

## Формальная верификация

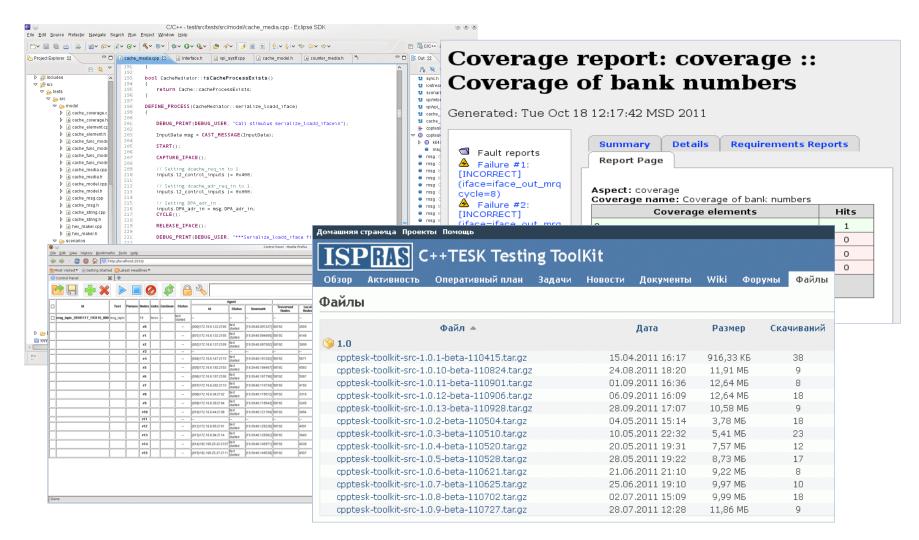

## Проект C++TESK

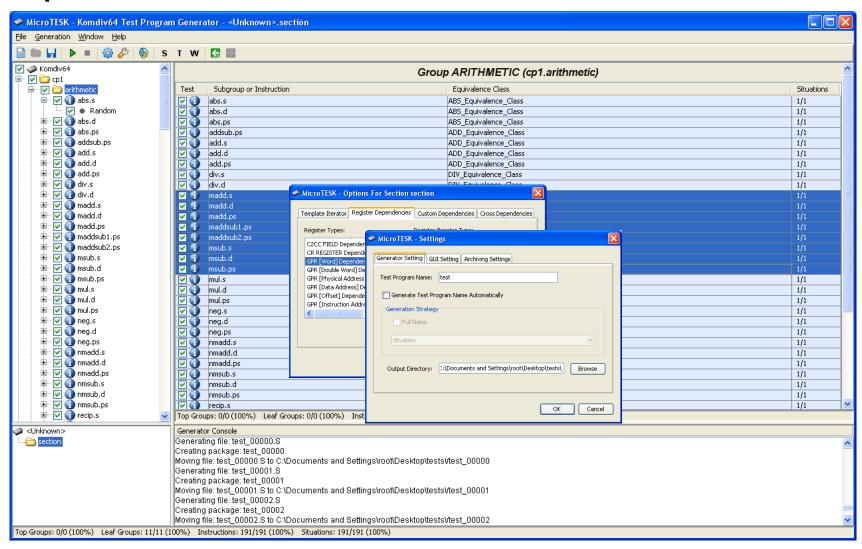

#### Проект MicroTESK

## Открытие проблемы

- Статический анализ HDL-кода, использование статического анализа в верификации

- Использование методов формальной верификации в имитационной верификации

- Распараллеливание процесса верификации, обработка графов сверхвысокой размерности

- Автоматическая локализация и диагностика ошибок в HDL-моделях

#### Контакты

- Институт системного программирования РАН (ИСП РАН) http://www.ispras.ru

- Верификация микропроцессоров @ ИСП РАН http://hardware.ispras.ru

- A.C. Камкин, с.н.с. ИСП РАН kamkin@ispras.ru

# Спасибо Вопросы?